��ICP��112451047180��-6

�����Ƽ�

��ϸ����

MEMS���ٶȼ��е�������ѹ�����

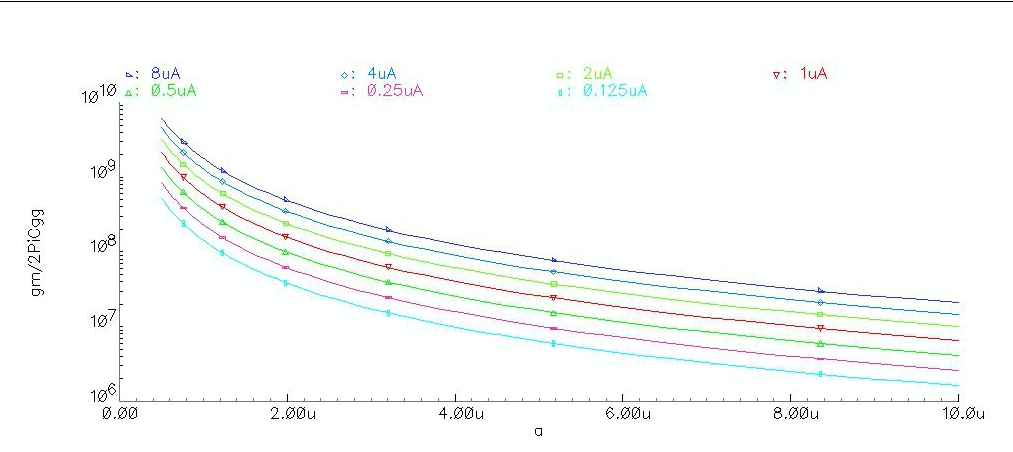

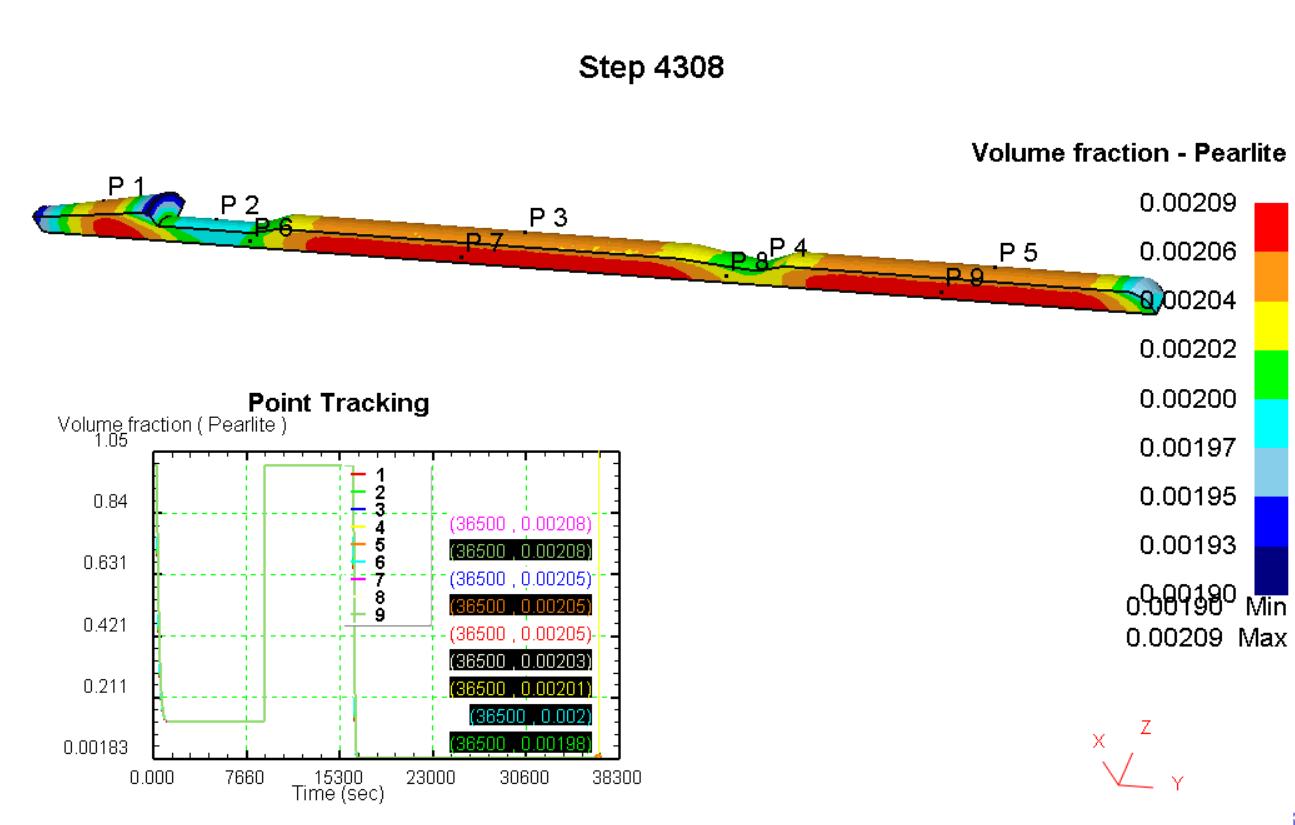

ժҪ��ѹ��������ѹ����Low Dropout Regulator����� LDO����Ϊ��Դ������·�IJ��֣���Խ��Խ�㷺��Ӧ�õ���Яʽ�ֳ��豸�У�������Ƭ��ϵͳ���ɵķ������������ڱ��ڼ��ɡ�Ӧ�ü��ص㣬������ LDO��LDO����Ϊ�ܶ�Ӧ�õ���Ҫѡ���봫ͳ��LDO��ȣ�LDO���ȶ��Ժ�˲̬�����ϴ����Žϴ�ȱ�ݣ����ȶ��Ժ�˲̬������������е������ս�����LDO���е�����ȱ�㣺���ؽϲ���ȶ��Ժ���������ʱ������˲̬��Ӧ�ٶȣ����������һ���ھ����������ȶ���Ҫ���ǰ�������LDO����˲̬��Ӧ�ٶȵĵ�·�����幤�������������һ�ֻ���SMIC0.13μmCMOS���յ���Ƭ������͵�ѹ��������ѹ����Ҫ�����ܹ�Ϊ���ֵ�·�����ṩ100mA���������ͬʱ�����кܵ͵�ѹ�����ߵ�PSRR���͵Ĺ��ġ����õ����������Լ����������Ӧ��������϶�������Ŵ����DZ�������еĺ���ģ�飬���ǵ�����ֱ�Ӿ�����LDO�����ܡ�Ϊ��ʹ��϶���ܹ�������1.4V��Դ��ѹ�²��Ҿ��кܸߵ�PSRR��������Դ�ͳ�ṹ�����е�ȱ�ݽ�������ϸ�ķ�����֤���Աȡ��Ľ��˸��ֵ�·���˽ṹ������ʵ�������Ҫ�����ͬʱ�����Ŵ������ö༶�Ŵ�ṹ������˻�·���棬�������ղ�����ʽ��֤�˻�·���ȶ��ԣ�Ϊ�����˲̬��Ӧ�������������ӱ��˲̬��ǿ��·������SMIC0.13μmCMOS�����£����������LDO��������϶����·������ƣ������spice���������˷�����֤���������������ڵ�Դ��ѹ����1.4V�£���LDO�ܲ���1.2V�������ѹ�������������ĸ��ص�����ΧΪ0.2mA��100mA��Dropout��ѹС��100mV��PSRR��@DC��С��-58dB��PSRR��@100kHz��С��-18dB����̬����С��75μA������ʱ��С��2μs�������ѹС��72mV���ؼ��ʣ�Capless��LDO��PSRR�����壬CMOS����Ŀ¼��һ������. 11.1 �о����������� 11.2 �������о���״�Լ���չ���� 21.2.1 �о���״ 21.2.2 ��չ���� 21.3 ���ĵ���Ҫ���������Ľṹ 3�ڶ��� LDO �Ļ������� 52.1 LDO ��� 52.2 LDO ����Ҫ���ܲ��� 62.2.1 ѹ�� 62.2.2 ��̬���� 62.2.3 ���ص����� 72.2.4 ���Ե����� 82.2.5 ˲̬���� 92.2.6 ���� 102.2.7 ��Դ���Ʊ� 112.3 LDO ָ���ȷ�� 112.4 �ܽ� 12�����´�϶����·�����. 133.1 ���˽ṹ�ķ�����ѡ�� 133.2 ��·������� 223.3 ������. 233.4 �ܽ� 28������ LDO ����� 294.1 ���˽ṹ�ķ�����ѡ�� 294.1.1 ���ʹܳߴ��ȷ�� 294.1.2 ������ֵ��ȷ�� 314.1.3 ���Ŵ����ṹ��ȷ�� 324.2 ��·������� 344.3 ������ 454.4 �ܽ� 58�����½���. 605.1 ���ĵ���Ҫ�������� 605.2 ��������չ�� 60�� л61�ο�����62��һ�� ����1.1 �о�����������Ŀǰ����Դ����оƬ�ѱ��㷺Ӧ�����ִ�����ϵͳ�У���Դ����оƬ��һ���ⲿ��ѹ������﮵�������ѹ��220V�����磩ͨ��������Ƶĵ�·��ת����û���Ҫ�ĵ�ѹ����Դ����оƬ���·�Ϊ�������֣�����AC��DC��AC��AC��DC��AC��DC��DC������һ����DC��DCоƬ����Ӧ�û����IJ�ͬ����������������Ҫ�ķ��ࣺ��1����п���ʽDC-DC�任�������ŵ�ת��Ч�ʷdz��ߣ���������ʹ�������Ըߵ͵�ƽ���ƹ��ʹܵĵ�ͨ��ضϣ�ʹ�������ѹë�̷dz���ʹ����dz�����˲����ݣ�Ҳ�����˵����ë�̵�ѹ�ĵ�Ƶ�ɷ֣����Ե�п���ʽDC-DC�任�����������ܷdz������û�Ҫ����Ӧ���ڵ������������Ǹñ任���������û�Ҫ��2����ɱ�ʽ��ѹ�任�����������Ǽȿ�������������ѹ��ĵ�ѹ���ֿ�������������ѹС�ĵ�ѹ��Ҳ����˵����������ѹ��С��ȫ�����������Լ��ȱ��Ҳ�����ԣ��Ǿ��������ѹ������ŷdz�����������ţ����п���ʽDC-DC�任��һ������ɱ�ʽ��ѹ�任���������ڶ�����Ҫ��ܸߵij��ϡ���3��LDO������ѹ��������Ҫ�ŵ���кܵ��������ܣ�ȱ���������ѹֻ�ܵ��������ѹ������������ѹ�任[1-4]�����п���ʽDC-DC�任���͵�ɱ�ʽ��ѹ�任����ȣ�LDO������ѹ�����е����Ʋ����ǵ͵����������ѹ��������ԼĽṹ����С�IJ�Ʒ����ͽϵ͵ľ�̬���ġ����LDO������������ܱ�����ʦ��Ӧ���ڿɳ�ʽ����ϵͳ�У���Ϊ�˵�Դ����оƬ����ͷ������ͳLDO�����������Ƭ��������ݣ��������һ��������Ч���裨ESR�����õ���ΪLDO��·�ṩ��һ�����ƽ����㣬�����������ϵͳ����λԣ�Ⱥ�����ԣ�ȣ��Ӷ�����˻�·���ȶ��ԣ����������ӵ��ݵĴ��ڻ�����PCB��������������ϵͳ�ijɱ����ӳ̶ȡ�����������LDO�����Խ����“�Ӵ�”����ӵ���ȥ����ΪPCB��ʡ�˿ռ䣬������PCB���֣����Ǵ��������������ڲ�����Ƥ���ĸ��ص��ݻή��ϵͳ���ȶ��ԣ�����ʹ�������ܱ���ˣ�����ʦ���������������Ƭ����ݲ��Ҿ��������ȶ��Ժͽϵ������������Ƭ������͵�ѹ��������ѹ����LDO�����÷���Ŀǰ�Ѿ���Ϊ����������ѹ��������ȵ���ѵ㣬������Զ�����塣1.2�������о���״�Լ���չ����1.2.1�о���״�����LDO��ƷƷ�ֶ࣬����ǿ����������ԭ����ɵģ����ȣ���������IC��ƹ�˾�����ż�ʮ���ƾõĿ��д��У��ۺ�ļ�������ʹ�����ڰ���LDO֮�ڵļ�������ģ��IC����ңң���ȣ���Σ�����ģ��IC���칤�շdz��Ƚ���ר��Ϊģ��IC�����ĸ������������������ģ��IC��Ʒ����ھ�����������Ī�������磬��������������˾��TI��������TPS736�Ȳ�Ʒ������TI���е��Ƚ�CMOS��������������NMOS��Դ������Ϊ���ʹܣ�����ѹ��Ϊ75mV����10Hz��100kHzƵ���ڵ����������ѹ�ʹ�30μV�������ѹ�仯���¶ȱ仯�Լ����ص����仯�������ѹ��Ӱ�����Ϊ1%����������ɴ�400mA�����ͬʱ����������������˾��TI��������TLV713������LDO��ʵ��������κ���ֵ�ĵ��ݶ����Ա���ϵͳ�ȶ����侲̬����ֻ�в���40μA��1kHzʱ��Դ���Ʊȴﵽ��-85dB��������˾������LDO����Ҳ�dz��Ƚ�������ADI��ADP3338��ѹ��������ѹ������������ߴ�1A�����������Ϊ1Aʱѹ��С��200mV����оƬҲʵ��������Ƭ�⸺�ص��ݼ��ɱ���ϵͳ�ȶ����ص㡣�ò�Ʒ�����dz��͵��������ܡ��ߵĵ�Դ���������Ϳɵ������ѹ�����Ƽ�������һ������ڹ����˾�����ڵ�LDO�����ǹ���ˮƽ���ǵ�·���ˮƽ���������IC��ͷ������ԣ����ڽ���������У�����磺�廪��ѧ��������ѧ��������ѧ�����ӿƼ���ѧ���Ͳ����з����������磺�е�Ƽ�����24�������ڽ����Ŵ����Ʒ���з����顣��С����˾�IJ������ü�ޡ�1.2.2��չ������1����������SOC��SystemOnaChip���У����ڼ��ɶȸߣ�ģ���·�����ֵ�·֮��ļ��dz�С�����Ž������������࣬��ͼ����ҲԽ��Խ���ӣ����ɱ����������Խ��Խ��ļ������ݣ������ֵ�·������ʱ���źź�����ͨ��������֮�����ϵ��ݴ�����Դ�����µ�Դ��ѹ��С�仯������LDO��·����Ҳ������ɾ���ܺ͵��������������˸������ɵ�������ѹ����Դ������LDO������������ѹ������һ��Ӱ����LDO���������ܣ���LDO�У����ڸ��ص��ݼ�С�˼�������������Ƶ�����������ӡ�������Ƶ�����LDO��ģ���·����ߵĿ���Խ��Խ����2�����ٵ�˲̬��Ӧ�����ص���ͻ��ʱ���ܵ�LDO���Ŵ�������ת�����ʺ����Ļ�·���������ƣ������ѹ���кܴ�Ĺ����С�ļ���������ijЩӦ�û����л�ֱ��Ӱ�������·�����ܣ�Ϊ�˼�С�����ѹ���塢���ָ̻�ʱ�䣬����ʦ�DZ�����Ƴ����п���˲̬��Ӧ������LDO��������ʵ��Ӧ������[8-10]����3������LDO�Ĺ���һ��ָ��̬���ģ�����һ���渺�ص����仯�ı������û�ϣ���ڲ�ͬ���ص����������£�LDO�����ֺܸߵ�Ч��[11-12]����Ȼ��С�˾�̬���Ŀ������LDO��Ч�ʣ�����LDO�Ļ�·������ƫ�õ������ɱ�����½�������LDO��ת�����ʽ��ͣ������˵����ص����仯ʱ�����ѹ����Ӧʱ�䡣����ͨ���Ż���·�������ߴ��µ�·�ṹ�����ٶȺ���֮����һ����[13-19]��1.3���ĵ���Ҫ���������Ľṹ���ĵ���Ҫ���������һ�ֻ���SMIC0.13μmCMOS���յ���Ƭ������͵�ѹ��������ѹ����Ҫ�����ܹ�Ϊ���ֵ�·�����ṩ100mA���������ͬʱ�����кܵ͵�ѹ�����ߵ�PSRR���͵Ĺ��ġ����õ����������Լ����������Ӧ��������϶�������Ŵ����DZ�������еĺ���ģ�飬���ǵ�����ֱ�Ӿ�����LDO�����ܡ�Ϊ��ʹ��϶���ܹ�������1.4V��Դ��ѹ�²��Ҿ��кܸߵ�PSRR��������Դ�ͳ�ṹ�����е�ȱ�ݽ�������ϸ�ķ�����֤���Աȡ��Ľ��˸��ֵ�·���˽ṹ������ʵ�������Ҫ�����ͬʱ�����Ŵ������ö༶�Ŵ�ṹ������˻�·���棬�������ղ�����ʽ��֤�˻�·���ȶ��ԣ�Ϊ�����˲̬��Ӧ�������������ӱ��˲̬��ǿ��·���������ƵĻ����ϣ�����cadence��spectre���湤�߶�LDO��������Ҫ���ܽ�������ϸ�ķ�����Աȡ����Ĺ���Ϊ���£�������֯���£���һ�£������˿�����о����������壬�����˹�����LDO���о���״�ͷ�չ���ƣ����������ĵ���Ҫ�����Լ���֯�ṹ���ڶ��£���Ҫ������LDO�Ļ������ۣ���ѹ����DropoutVoltage������̬������QuiescentCurrent�������ص����ʣ�LoadRegulation�������Ե����ʣ�LineRegulation����˲̬���ԣ�TransientResponse����������Noise������Դ���Ʊȣ�PowerSupplyRejectionRatio�������ָ���������ϸ�ķ�������ܡ������£������ΪLDO�ṩ����ѹ�Ĵ�϶����·��Ϊ��ʹ��϶���ܹ�������1.4V��Դ��ѹ�²��Ҿ��кܸߵ�PSRR��������Դ�ͳ�ṹ�����е�ȱ�ݽ�������ϸ�ķ�����֤���Աȡ��Ľ��˸��ֵ�·���˽ṹ������ʵ�������Ҫ������������ܲ�����������ɣ�����������Ӧ�ķ������������£����Ӧ�û���ȷ����LDO�����ָ�꣬���������ָ�������ѡ���˺��ʵ����˽ṹ��������Ƴ�����Ӧ�û���Ҫ��ĵ�·���������ƵĻ����ϣ�����cadence��spectre���湤�߶�LDO��������Ҫ���ܽ�������ϸ�ķ�����Աȡ������£��Ա��ĵ���Ҫ�����������ܽ��չ����