苏ICP备112451047180号-6

加速度传感器计步器设计与实现

摘要

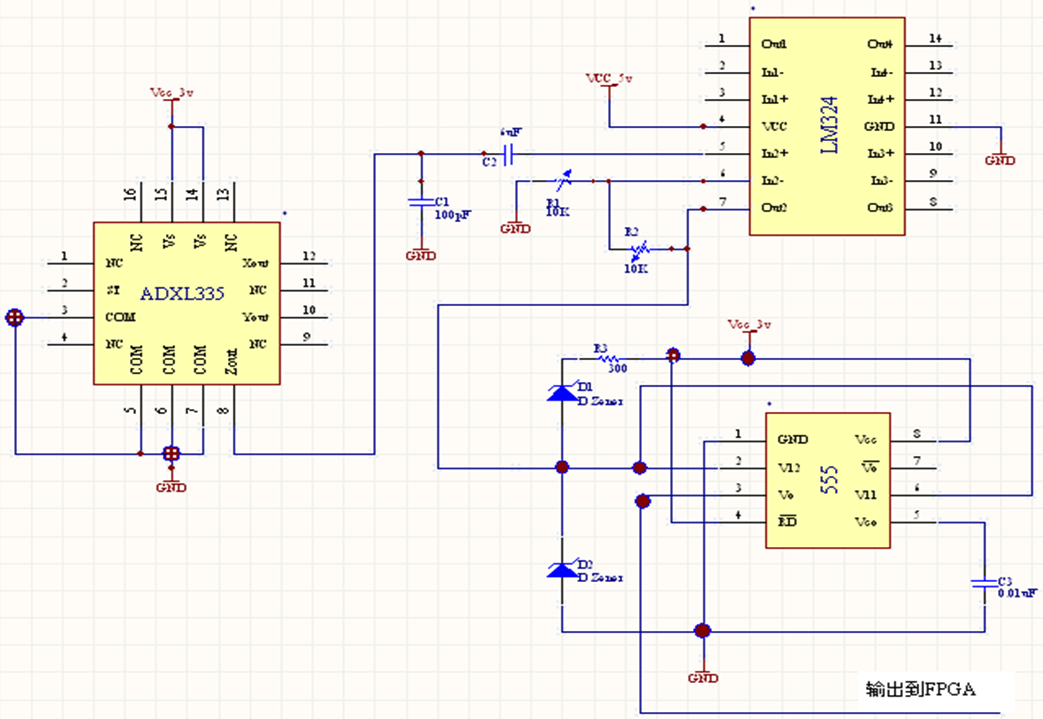

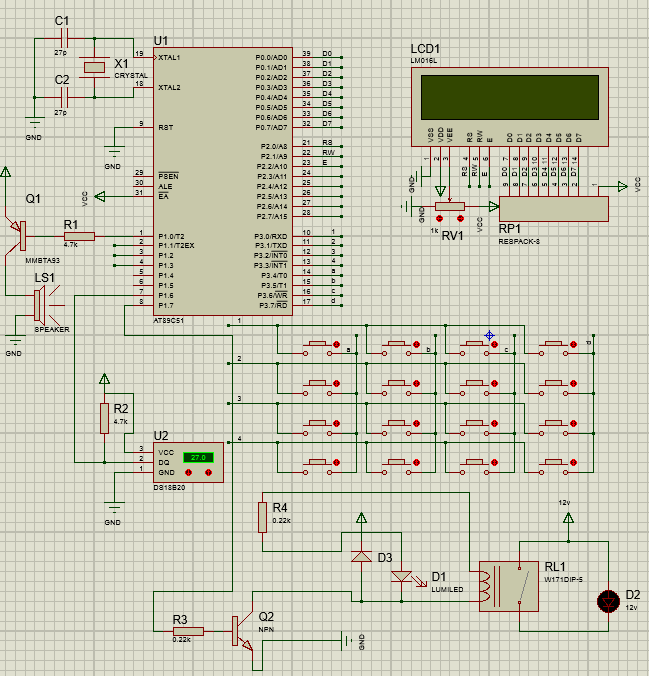

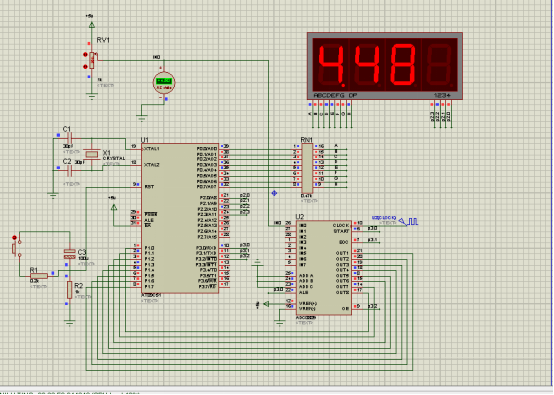

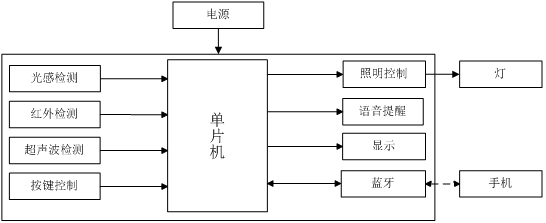

本实验的目的是计步器的设计实现,要求实现基于ADXL335型加速度传感器、555电路及FPGA、具有置零、累加计数功能的数字计步器,并采用2位数字显示步数。加速度传感器在运动时,随着加速度的变化会产生脉冲信号,这个信号经过波形放大之后,通过施密特触发器整形,会得到标准的方波脉冲。标准的方波输入到FPGA中,通过VHDL编程,实现对输入信号中脉冲个数的计数,并控制数码管,实时的将脉冲个数显示出来,实现计步。通过本实验可以让学生掌握电子电路设计、调试的一般方法,进一步提高实践动手能力,为今后的学习和工作打下良好的基础,同时培养分析问题、解决问题的能力,很有必要进行一项实验课程。

关键字:数字计步器 加速度传感器 FPGA

目录

摘要 ……………………………………………………… 1

第一章 实验任务与原理 ……………………………… 3

1.1任务指标及功能需求 ……………………………… 3

1.3原理阐述 ………………………………………… 3

1.4主要元件介绍 …………………………………… 3

第二章 设计思路及方案 ……………………………… 6

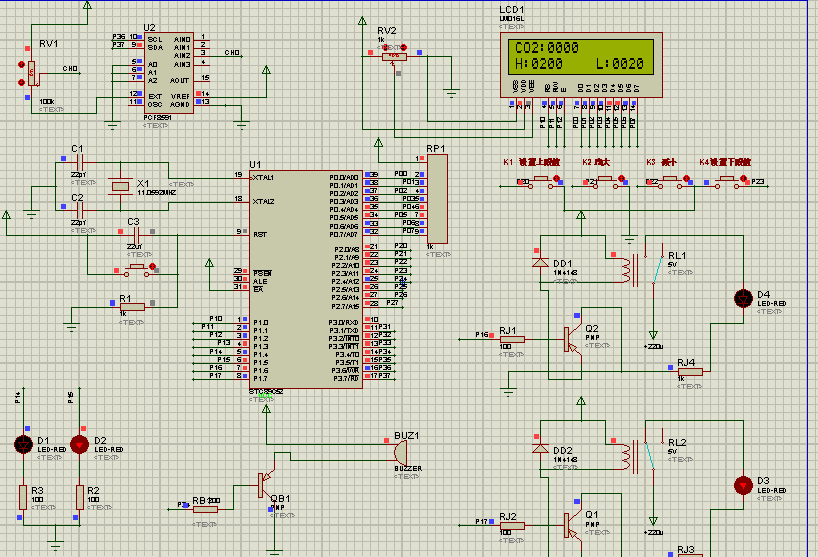

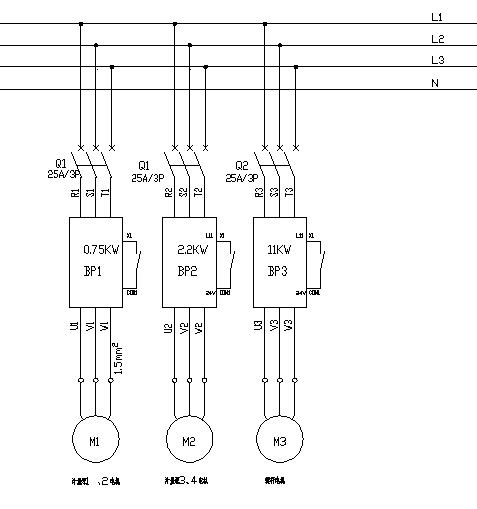

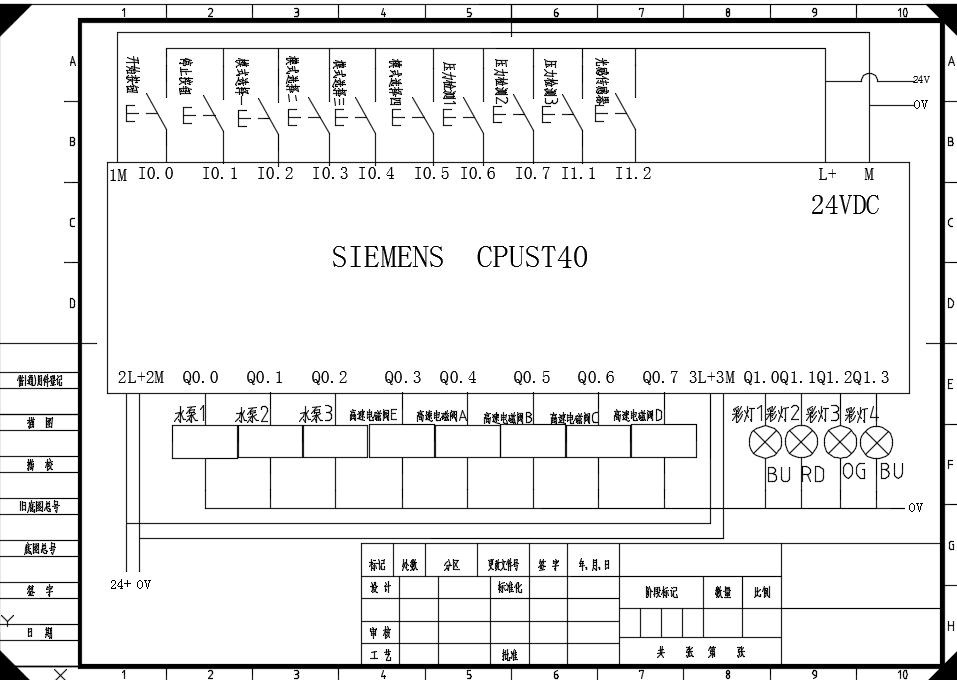

第三章 硬件设计与装配 ……………………………… 7

3.1模块设计 …………………………………………… 7

3.2整体硬件电路的布线装配…………………………… 9

第四章 FPGA模块程序设计 …………………………… 10

4.1程序总体设计框图 ………………………………… 10

4.2模块说明及部分代码 ……………………………… 9

第五章 系统调试 ……………………………………… 12

5.1调试 ………………………………………………… 12

5.2排故 ………………………………………………… 13

第六章 结束语 ………………………………………… 14

附录 …………………………………………………… 15

源程序代码 ……………………………………………… 15

参考文献 ………………………………………………… 17

参考文献

[1] 白中英. 数字逻辑与数字系统(第四版 立体化教材). 北京: 科学出版社, 2008年

[4] 李大友. 数字电路逻辑设计. 北京:清华大学出版社, 1997年