��ICP��112451047180��-6

��ϸ����

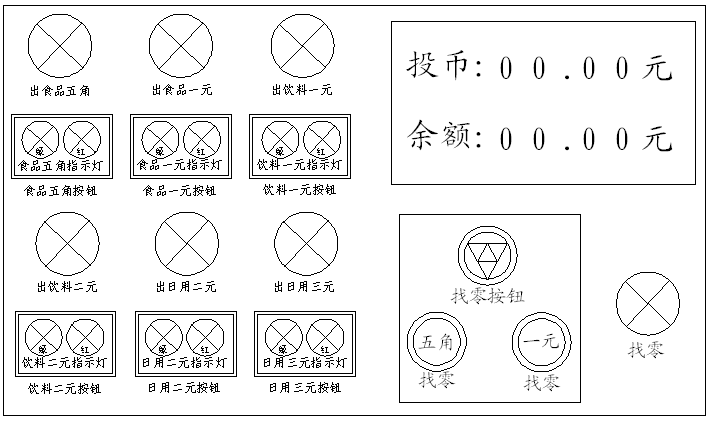

����EDA����������ʽ�������������

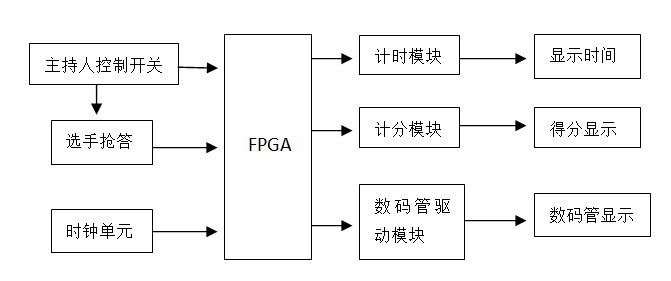

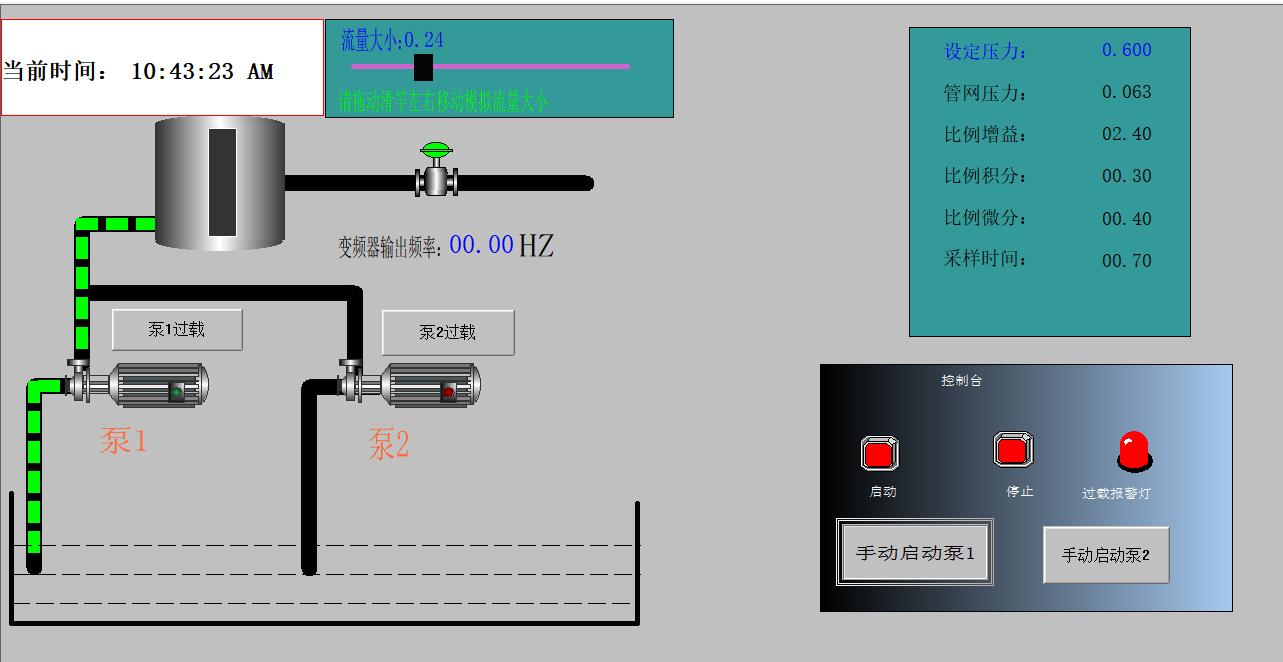

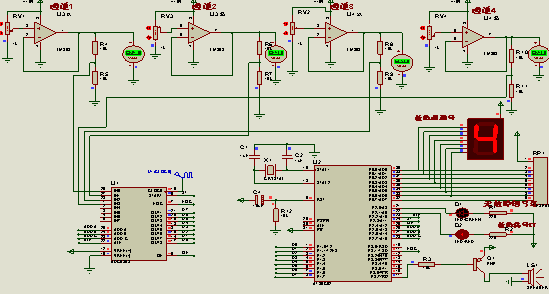

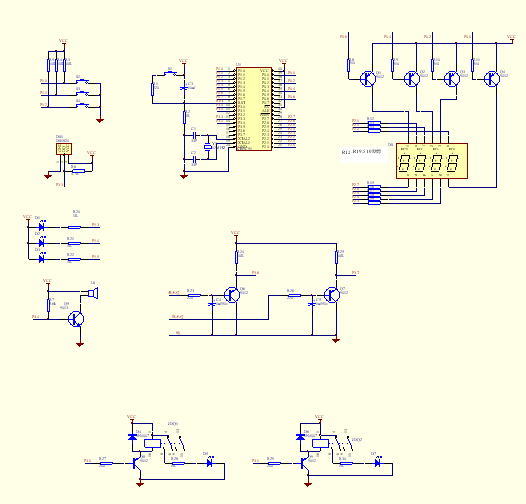

ժҪ�����ο������������ʽ4·������������·����һ��EDA������Verilog HDL������FPGA��Quartus����Ƶģ�ͬʱ��4·��������·���������ʾ����������������ƿ���ͬʱ������ѡ�ֻ���֧�����ڱ����н���������4����ťa��b��c��d���õĸ�λ����������������ϵͳ���ƿ����н��п��ơ�������˵����ʱ����ʱ����30����ʱ������������ɹ�ʱ������ʱ�䣬��ʱѡ�ֺ��������������ʾ����֮��Ӧ��LED��Ҳ������������˽�ͨ�����ƼӼ������ж�ѡ�����Ƿ�ش���ȷ���Ӽ��֡��ڱ��������������˰��¸�λ�������˼Ʒ�ģ������ģ�鶼Ϊ��һ�ֵı�����������ϵͳ��Ҫʹ�õ���оƬEP2C8Q208��ͨ��ϵͳ���𡢼�ʱ����Ƶ�����Ʒ֡����桢�����������ģ�飬Ȼ���̺ͷ������ʵ�������������Ҫ�Ӷ���������ܡ��ؼ��ʣ���������������ʾ��Ӳ���������ԣ��ɱ����������Ŀ¼��1�� ���� 11.1 ѡ�ⱳ�� 11.1.1 EDA������չ 11.1.2 �����о��ı�Ҫ�� 21.2 �о���������� 2��2�� ϵͳ������� 42.1 FPGA��� 42.1.1 FPGAоƬ�ṹ 42.1.2 FPGA������� 72. 2 Verilog HDL���� 82.2.1 Verilog HDL��� 82.2.2 Verilog HDL��Ҫ���� 92.2.3 Verilog HDL��VHDL������ 92.3 ������������Ʒ��� 102.3.1 ���������� 102.3.2 ����������ԭ�� 11��3�� ������ģ�������ʵ�� 113.1 �����б�ģ�� 113.2 ���������ģ�� 133.3 ��ʱģ�� 153.4 ��Ƶ��ģ�� 163.5 �Ʒ�ģ�� 163.6 ����ģ�� 173.7 ����ģ�� 17��4�� ������������ơ�ʵ������� 194.1 �����б������� 194.2 ���������ģ�������� 214.3 ��ʱģ�������� 224.4 ��Ƶģ�������� 244.5 �Ʒ�ģ�������� 254.6 ����ģ�������� 29�� �� 31�ο����� 32����¼ 34��1�� �� ��§1.1ѡ�ⱳ��§1.1.1EDA������չEDA�����ǵ�������Զ���������ָ�ڿɱ���������Ϊ����Ļ�����,��HDLΪ���﷽ʽ,�Լ����,�ɱ������������Ϊ��ƹ���,ͨ�����������Զ���ɵ���ϵͳ������ƣ������γ�һ���������ɵ���ϵͳ.ͨ��ʹ��EDA�����ʦ��ͨ���Ӷ��ֽǶ���Ƶ���ϵͳ���Ե��Ӳ�Ʒ���з���������Զ����ICͼ������PCB�ӹ���·���ܣ������дֹ��������ɼ������ɡ�Protel��Altium Designer��PSPICE��multisim12(ԭEWB�����°汾)��OrCAD��PCAD��LSIIogic��MicroSim��ISE��modelsim��Matlab�Ⱦ���Ӱ���EDA������ϵͳ�������������Ϳɱ��оƬ���������������Щ��������ǿ�����ڶ������������ʵ�ֵ�·���������棬���ҿ��Խ���PCB���Զ����ߣ�����������ļ��ĵ����������ӿڡ�����ϵͳ���ͨ��ʹ��EDA����Ӧ�߱������ص㣺(1)���������ת��ΪӲ��ϵͳ��(2)��ƹ����п���������������������(3)ϵͳ�������ֳ����б༭��Ҳ��������������(4)����ϵͳ�����Ժã����С�����ĵͣ�(5)��Ƶ���ֲ�Ժã�Ч�ʸߣ�(6)�Ƚ��ʺϷֹ�����Լ������������ˣ�EDA�������ִ�������Ƶķ�չ���ơ�§1.1.2�����о��ı�Ҫ�����ںö����������Dz����˵�Ƭ����ֻ������������������оƬ�ʹ����������������ѡ��ڶ��ַ������������������ơ�����������оƬ�ʹ������ĵ�·���������ʽ����������Ҫ�ɵ���Ԫ������ɣ�ͨ�����롢����ͽ��뽫�����ź���ʾ������ͨ�������غ�ϵͳ���Ƶ�·�����������źŵ�·��ͨ����ʱ��������������źţ�ʵ�ֶ�ʱ���ܡ���Ȼ���ֵ�·��ɵIJ������ɱ��������ҹ�ģС���������ܼ�����·�����Ĺ����л���ֺܶ����⣬�����·�Ĺ滮��PCB��Ļ����Լ��������ȡ���������������Ʒ�������ʵ�ֵĻ������ܵ�Ӧ�����������������ľ����ԣ�һЩ����������ʵ�ֵġ�Ȼ��������FPGA������һЩ�ص㣬����FPGA����Ӧ�ߵ��ŵ���Կ˷���Щ���⡣FPGA��Ϊһ���¼��������������ƣ���1��FPGA���������ƴ��ģϵͳ����2��FPGA�ܵÿ졣��3��FPGA�ڲ�������Բ������д������Ӻ�������4��FPGA�д��������ˣ����Կ������Ρ�§1.2�о�������������ο����о�����Ҫ����������������ͬʱ������ѡ�ֻ���֧�����ڱ����н���������4����ťa��b��c��d���õĸ�λ����������������ϵͳ���ƿ����н��п��ơ�������˵����ʱ����ʱ����30����ʱ������������ɹ�ʱ������ʱ�䣬��ʱѡ�ֺ��������������ʾ����֮��Ӧ��LED��Ҳ������������˽�ͨ�����ƼӼ������ж�ѡ�����Ƿ�ش���ȷ���Ӽ��֡��ڱ��������������˰��¸�λ�������˼Ʒ�ģ������ģ�鶼Ϊ��һ�ֵı������������ο�����[1]�����. ����FPGA��Ƕ��ʽ������Ӧ��. ���������ӹ�ҵ������, 2006: 1-200[2]���. ��ͨprotel DXP 2004��·���. ����: ���ӹ�ҵ�����磬2006: 1-200[3]����. Verilog HDL����ϵͳ��ƣ�ԭ����ʵ��������. ����: �������ӿƼ���ѧ�����磬2012: 1-150[4]��ʯ. ���ֵ��Ӽ�������������棩. ����: �ߵȽ���������, 2006: 386-455[5]�Һ��࣬������. ����EDA�����IJ�λ���Ʒ����ڵ����������е�Ӧ��.���ӹ���ʦ��2005��9����66—68[6]�����࣬�Ⱞƽ.����FPGA�Ķ�·�����������.�ִ���е��2006��6����37-38[7]���»�����֥��.����FPGA����������������ʵ�������ʵ��.ʵ�����о���̽����2008,27��3����36-39[8]��ռ��.����FPGA�������������������.���ڿƼ���2008��12����43-44[9]�����.�ɱ��������.�������������ӿƼ���ѧ�����磬2002[10]��㣬������������.����FPGA�Ķ�·�����������ʵ��.�㽭������ѧѧ����2010��27��2����249-254[11]����ȫ.���Ӽ�������ʵ����γ����. �й����������磬1999[12]�ź������Ƿ�.FPGA/CPLDӦ�����200��.�����������ʵ�����磬2009[13]������.CPLD/FPGAǶ��ʽӦ�ÿ����������ֲ�. �й�����������,2003,212-218[14]�������������.����CPLA/FPGA��VHDL���.��е��ҵ�����磬2006,28-65[15]̷�������Ų���.EDA������Ӧ��.�������ӿƼ���ѧ�����磬2002[16]�����ۣ�����.FPGAϵͳ�����ʵ��.�������������պ����ѧ�����磬2005[17]���캣������.VHDL����������ʵ������.������������ͨ��ѧ�����磬2008[18]������.VHDL���Լ���Ӧ��.�������ߵȽ��������磬2005[19]����.VHDL��FPGA���.�������й����������磬2003[20]������.Verilog HDL�����ʵ��.�������������պ����ѧ�����磬2012[21]����������.����Quartus II������ϵͳVerilog HDL���ʵ�����.���ӹ�ҵ�����磬2010[22]����.����Verilog HDL��FPGA����빤��Ӧ��.�����ʵ�����磬2009